# SP245-01

# Solidtron™ Solid State Initiator Firing Switch, C-Pak

**NOTICE:** This product is export controlled

## **Description**

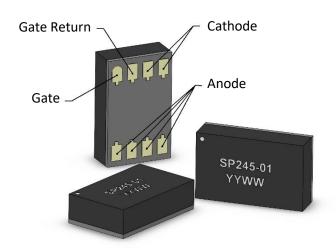

The **Solidtron™ SP245-01** is an advanced high-voltage current-controlled thyristor packaged in a **C-Pak** custom SMT package.

Like all Solidtron™ products, the internal semiconductor employs high cell density and an advanced termination design to achieve high peak current capability, low conduction loss, low off-state leakage, negligible turn-on delay jitter, and most importantly, extremely high turn-on dl/dt capability. It is ideally suited for a wide variety of capacitor discharge applications requiring precise timing and rapid energy transfer capability.

The C-Pak is a custom surface mount package in which the semiconductor is attached to a metalized ceramic substrate using 90Pb10Sn solder, wire bonded using 0.010" aluminum wire bonds, and then, encapsulated using Hysol FP4653 epoxy. The C-Pak is specifically designed to comply with IPC 2221 Section 6.3 Electrical Clearance (any elevation).

The SP245-01 is intended to replace triggered spark gaps of similar voltage and current ratings.

#### **Features**

- 1500V Repetitive Off-State Voltage

- VGK = 0V = OFF-STATE

- 100 kA/µs dI/dt capability

- Low Turn-on Delay Time

- Low Conduction Loss

- 3.5kA Repetitive Surge Current

#### **Applications**

- LEEFI detonators

- Electronic Safe and Arm Devices

- Ignition Safety Devices

- Firing Modules

- Capacitor Discharge Units

# Solidtron™ SP245-01

| Table 1 Maximum Ratings                                                       | Symbol                                 | Value       | Units              |  |

|-------------------------------------------------------------------------------|----------------------------------------|-------------|--------------------|--|

| Repetitive Peak Off-State Voltage                                             | $V_{DRM}$                              | 1500        | V                  |  |

| Repetitive Peak Reverse Voltage                                               | $V_{RRM}$                              | -10         | V                  |  |

| Off-State Rate of Change of Voltage Immunity (V <sub>D</sub> =1500V)          | dv/dt                                  | 1000        | V/μSec             |  |

| Peak Non-Repetitive Surge Current (1/2 Sinusoid Pulse Duration =/<300nSec)    | I <sub>TSM</sub>                       | 4000        | Α                  |  |

| Peak Repetitive Surge Current (1/2 Sinusoid Pulse Duration =/<300nSec)        | I <sub>TRM</sub>                       | 3500        | Α                  |  |

| Rate of Change of Current                                                     | dI/dt                                  | 100         | kA/μSec            |  |

| Critical Capacitor Discharge Event Integral (Underdamped LCR Circuit)         | I <sup>2</sup> t <sub>CRITICAL</sub>   | TBD         | A <sup>2</sup> sec |  |

| Repetitive Capacitor Discharge Event Integral (Underdamped LCR Circuit)       | I <sup>2</sup> t <sub>REPETITIVE</sub> | 2           | A <sup>2</sup> sec |  |

| Continuous Gate-Cathode Reverse Voltage                                       | $V_{GKS}$                              | -9          | V                  |  |

| Forward Peak Gate Current (10@Sec Duration)                                   | I <sub>GM</sub>                        | 10          | Α                  |  |

| Required Off-State Gate-Cathode Voltage                                       | $V_{GDM}$                              | 0           | V                  |  |

| Operating Junction Temperature Range                                          | TJ                                     | -55 to +125 | °C                 |  |

| Maximum Soldering Installation Temperature (See Moisture Sensitivity Caution) |                                        |             | °C                 |  |

| Storage Temperature Range (See Moisture Sensitivity & Solderability Cautions) |                                        |             | °C                 |  |

| Table 2 Electrical Characteristics                                      |                    |                                                                   |                       | Measurements |     |                    |         |

|-------------------------------------------------------------------------|--------------------|-------------------------------------------------------------------|-----------------------|--------------|-----|--------------------|---------|

| Parameter                                                               | Symbol             | Test Conditions                                                   |                       | Min          | Тур | Max                | Units   |

| Anode to Cathode Breakdown Voltage                                      | $V_{BR}$           | $V_{GK} = 0V, I_D = 100 \mu A, T_C \le 125^{\circ}C$              |                       | 1500         |     |                    | ٧       |

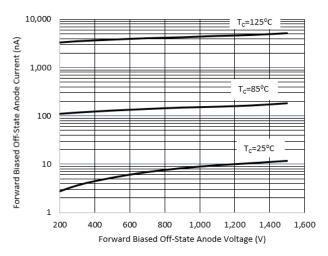

| Anode-Cathode Forward Off-State Current  See Figure 2.                  | I <sub>DRM</sub>   | V <sub>GK</sub> = 0V, V <sub>D</sub> =1500V                       | T <sub>C</sub> =-55°C |              |     | 60                 | nA      |

|                                                                         |                    |                                                                   | T <sub>C</sub> =25°C  |              | 10  | 100                | nA      |

|                                                                         |                    |                                                                   | T <sub>C</sub> =85°C  |              | 190 | 1000               | nA      |

|                                                                         |                    |                                                                   | T <sub>C</sub> =125°C |              | 5   | 10                 | μΑ      |

| Reverse Bias Gate-Cathode Breakdown Voltage                             | $V_{GRRM}$         | I <sub>GM</sub> =150μA, T <sub>C</sub> ≤ 125°C                    |                       | 9            | 10  |                    | ٧       |

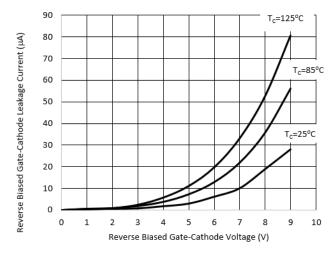

| Nine Volt Reverse Bias Gate-Cathode Leakage<br>Current<br>See Figure 1. | I <sub>GM</sub>    | V <sub>GK</sub> = -9V                                             | T <sub>C</sub> =25°C  |              | 28  |                    | μΑ      |

|                                                                         |                    |                                                                   | T <sub>C</sub> =85°C  |              | 57  |                    | μΑ      |

|                                                                         |                    |                                                                   | T <sub>C</sub> =125°C |              | 80  |                    | μΑ      |

| Two Volt Reverse Bias Gate-Cathode Leakage Current See Figure 1.        | I <sub>GM</sub>    | V <sub>GK</sub> = -2V                                             | T <sub>C</sub> =25°C  |              | 0.8 | 2                  | μΑ      |

|                                                                         |                    |                                                                   | T <sub>C</sub> =85°C  |              | 1.9 | 4                  | μΑ      |

|                                                                         |                    |                                                                   | T <sub>C</sub> =125°C |              | 2.4 | 6                  | μΑ      |

| Gate Trigger Voltage                                                    | V <sub>GT</sub>    | V <sub>D</sub> = 12V, I <sub>D</sub> =1mA                         | T <sub>C</sub> =25°C  | 450          | 500 |                    | mV      |

|                                                                         |                    |                                                                   | T <sub>C</sub> =85°C  | 250          | 350 |                    | mV      |

|                                                                         |                    |                                                                   | T <sub>C</sub> =125°C | 200          | 250 |                    | mV      |

| Gate Trigger Current                                                    | I <sub>GT</sub>    | V <sub>D</sub> = 12V, I <sub>D</sub> =1mA, T <sub>C</sub> ≤ 125°C |                       |              |     | 100                | μΑ      |

| Turn-on Delay Time                                                      | t <sub>d(ON)</sub> | 0.15μF Capacitor Discl                                            |                       | 30           | 60  | nSec               |         |

| Rate of Change of Current                                               | dI/dt              | $T_C=25^{\circ}C$ , $I_{GT}=500$ mA,                              |                       |              | 65  |                    | kA/μsec |

| Capacitor Discharge Event Integral                                      | l <sup>2</sup> t   | V <sub>DD</sub> =1200V, L <sub>S</sub> =15nH,                     |                       | 1.38         |     | A <sup>2</sup> sec |         |

| Peak Anode Current                                                      | I <sub>DM</sub>    | $R_S=0.010\Omega=CVR$                                             |                       | 3.2          |     | kA                 |         |

# Solidtron™ SP245-01

Figure 1 Typical Reverse Biased Gate-Cathode Leakage Characteristic

**Figure 2** Typical Forward Biased

Off-State Anode-Cathode Leakage Characteristic

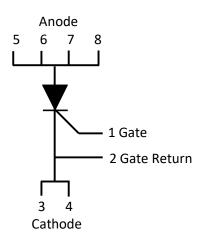

#### **Usage**

The Gate Return pad provides a dedicated connection directly to the cathode of the semiconductor die. This connection consists of a single 0.010" aluminum wire bond. Using the Gate Return pad as an independent gate driver return path reduces V=L\*dI/dt stress on the gate driver components. With C-Pak Solidtron™ devices, the Gate Return may, alternatively, be used as an additional Cathode pad; however, its internal connection possesses only 40% of the I²t capability of each of the other Cathode pads. Using it in this fashion must be qualified by the customer for their specific application.

#### **ESD Sensitivity**

The SP245-01 has been tested IAW MIL-STD-883 ESD-HBM (Human Body Model) to +/-2000V (Class 1C).

The SP245-01 has been tested IAW ANSI/ESDA/JEDEC/JS-002-2014 for ESD-CDM (Charged Device Model) to +/-1500V (Class C5).

## **Moisture Sensitivity**

The SP245-01 have been tested IAW IPC/JEDEC J-STD-020 and are classified as MSL Level 5A.

In accordance with IPC/JEDEC J-STD-033, C-Pak products are dry-baked and immediately packed in a Moisture Barrier Bag (MBB) containing desiccant and a Humidity Indicator Card (HIC). When the Moisture Barrier Bag is opened or compromised refer to IPC/JEDEC J-STD-033 for proper HIC interpretation, floor life and storage procedures.

Although IPC/JEDEC J-STD-033 prescribes specific dry-baking temperatures and times, caution is advised as additional baking of C-Pak SMD packages may cause oxidation and/or intermetallic growth of the terminations which may result in solderability problems during board installation. The temperature and time for baking this SMD package should, therefore, be limited with solderability considerations in mind. If available, it is recommended C-Paks be baked in a nitrogen or vacuum oven to limit exposure to oxygen during the baking process.

# **Solderability**

Although the component pads of the **SP245-01** appear to be gold plated, exposure to high process temperatures within the manufacturing process have accelerated the diffusion of the underlying nickel into and through the thin exterior gold surface, therefore, rendering the pads **subject to oxidation growth** if exposed to circumstances which

#### www.excelitas.com

# Solidtron™ SP245-01

#### **Solderability (Continued)**

promote nickel oxidation. Such circumstances should be avoided; otherwise, solderability of the **SP245-01** will be compromised.

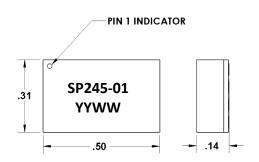

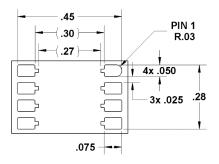

# **Markings and Dimensions**

#### **DIMENSIONS ARE IN INCHES**

TOLERANCES UNLESS OTHERWISE NOTED:

TWO PLACE DECIMAL +/- 0.010"

THREE PLACE DECIMAL +/- 0.005"

## PART NUMBER

SP = SOLIDTRON™ PRODUCT 245 = CHIP TYPE -01 = PACKAGE TYPE

#### DATE CODE

YY = LAST 2 DIGITS OF CALENDAR YEAR WW = WORK WEEK

## **About Excelitas Technologies**

Excelitas Technologies® is a photonics technology leader focused on delivering innovative, high-performance, market-driven solutions to meet the lighting, optronics, detection and optical technology needs of our OEM customers. Serving a vast array of applications across biomedical, scientific, safety, security, consumer products, semiconductor, industrial manufacturing, defense and aerospace sectors, Excelitas stands committed to enabling our customers' success in their end-markets. Our photonics team consists of 7,000 professionals working across North America, Europe and Asia, to serve our customers worldwide.

## **Excelitas Technologies**

Solidtron™ Products 284 Great Valley Parkway Malvern, Pennsylvania 19355 USA Telephone: (+1) 937.865.3800

aes@excelitas.com

For a complete listing of our global offices, visit www.excelitas.com/locations

© 2020 Excelitas Technologies Corp. All rights reserved. The Excelitas logo and design are registered trademarks of Excelitas Technologies Corp. All other trademarks not owned by Excelitas Technologies or its subsidiaries that are depicted herein are the property of their respective owners. Excelitas reserves the right to change this document at any time without notice and disclaims liability for editorial, pictorial or typographical errors.